### INTEGRATED CIRCUITS

# DATA SHEET

### P80CL410; P83CL410 Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

Product specification Supersedes data of 1995 Jan 20 File under Integrated circuits, IC20 1997 Apr 10

### Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

### P80CL410; P83CL410

| CONTEN         | ITS                                                     | 14.3.2           | Interrupt Enable Register (IEN1)                                    |

|----------------|---------------------------------------------------------|------------------|---------------------------------------------------------------------|

| 1              | FEATURES                                                | 14.3.3           | Interrupt Priority Register (IP0)                                   |

| 2              | GENERAL DESCRIPTION                                     | 14.3.4<br>14.3.5 | Interrupt Priority Register (IP1) Interrupt Polarity Register (IX1) |

| 2.1            | ROMless version: P80CL410                               | 14.3.6           | Interrupt Request Flag Register (IRQ1)                              |

|                |                                                         | 15               | OSCILLATOR CIRCUITRY                                                |

| 3              | APPLICATIONS                                            | 16               | RESET                                                               |

| 4              | ORDERING INFORMATION                                    | 16.1             | External reset using the RST pin                                    |

| 5              | BLOCK DIAGRAM                                           | 16.2             | Power-on-reset                                                      |

| 6              | FUNCTIONAL DIAGRAM                                      | 17               | SPECIAL FUNCTION REGISTERS                                          |

| 7              | PINNING INFORMATION                                     |                  | OVERVIEW                                                            |

| 7.1            | Pinning                                                 | 18               | INSTRUCTION SET                                                     |

| 7.2            | Pin description                                         | 19               | LIMITING VALUES                                                     |

| 8              | FUNCTIONAL DESCRIPTION OVERVIEW                         | 20               | DC CHARACTERISTICS                                                  |

| 8.1            | General                                                 | 21               | AC CHARACTERISTICS                                                  |

| 8.2            | CPU timing                                              | 22               | P85CL000HFZ 'PIGGY-BACK'                                            |

| 9              | MEMORY ORGANIZATION                                     | 22               | SPECIFICATION                                                       |

| 9.1            | Program Memory                                          | 22.1             | General description                                                 |

| 9.2<br>9.3     | Data Memory Special Function Registers (SFRs)           | 22.2             | Feature differences/additional features of                          |

| 9.4            | Addressing                                              |                  | P85CL000HFZ with respect to P83CL410                                |

| 10             | I/O FACILITIES                                          | 22.3             | Common specification/feature differences                            |

| 10.1           | Ports                                                   |                  | between P85CL000HFZ and P83CL410/P80CL51                            |

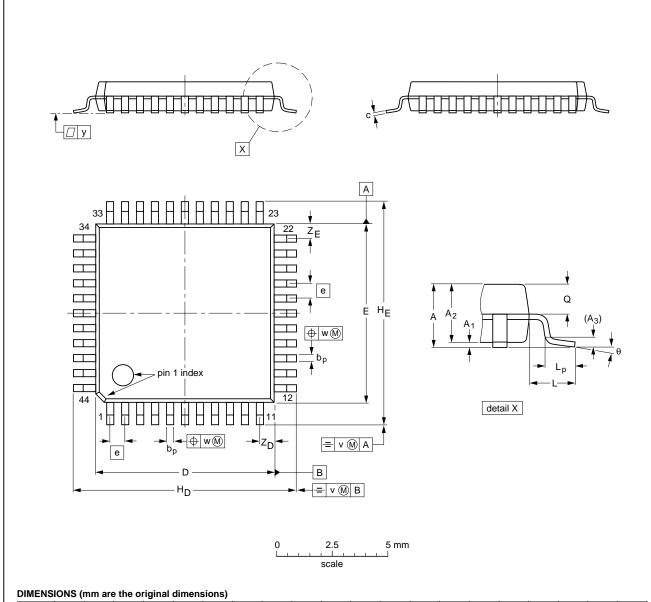

| 10.1           | Port options                                            | 23               | PACKAGE OUTLINES                                                    |

| 10.3           | Port 0 options                                          | _                |                                                                     |

| 10.3.1         | External memory accesses                                | 24               | SOLDERING                                                           |

| 10.3.2         | I/O Accesses                                            | 24.1<br>24.2     | Introduction<br>DIP                                                 |

| 10.4           | SET/RESET options                                       | 24.2.1           | Soldering by dipping or by wave                                     |

| 11             | TIMERS/EVENT COUNTERS                                   | 24.2.2           | Repairing soldered joints                                           |

| 12             | REDUCED POWER MODES                                     | 24.3             | QFP                                                                 |

| 12.1           | Idle mode                                               | 24.3.1           | Reflow soldering                                                    |

| 12.2           | Power-down mode                                         | 24.3.2           | Wave soldering                                                      |

| 12.3<br>12.3.1 | Wake-up from Power-down mode Wake-up using INT2 to INT9 | 24.3.3<br>24.4   | Repairing soldered joints Reflow soldering                          |

| 12.3.1         | Wake-up using RST                                       | 24.4<br>24.5     | Wave soldering                                                      |

| 12.3.2         | Power Control Register (PCON)                           | 24.6             | Repairing soldered joints                                           |

| 12.5           | Status of external pins                                 | 25               | DEFINITIONS                                                         |

| 13             | I <sup>2</sup> C-BUS SERIAL I/O                         | 26               | LIFE SUPPORT APPLICATIONS                                           |

| 13.1           | Serial Control Register (S1CON)                         |                  |                                                                     |

| 13.2           | Serial Status Register (S1STA)                          | 27               | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                     |

| 13.3           | Data Shift Register (S1DAT)                             |                  |                                                                     |

| 13.4           | Address Register (S1ADR)                                |                  |                                                                     |

| 14             | INTERRUPT SYSTEM                                        |                  |                                                                     |

| 14.1           | External interrupts INT2 to INT9                        |                  |                                                                     |

| 14.2           | Interrupt priority                                      |                  |                                                                     |

| 14.3           | Interrupt registers                                     |                  |                                                                     |

Interrupt Enable Register (IEN0)

14.3.1

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

#### 1 FEATURES

- Full static 80C51 Central Processing Unit

- 8-bit CPU, ROM, RAM, I/O in a 40-lead DIP, 40-lead VSO or 44-lead QFP package

- 128 bytes on-chip RAM Data Memory

- 4 kbytes on-chip ROM Program Memory for P83CL410

- External memory expandable up to 128 kbytes: RAM up to 64 kbytes and ROM up to 64 kbytes

- Four 8-bit ports; 32 I/O lines

- Two 16-bit Timer/Event counters

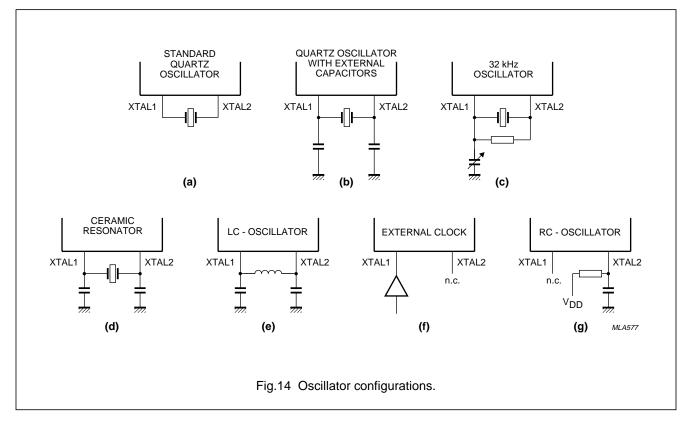

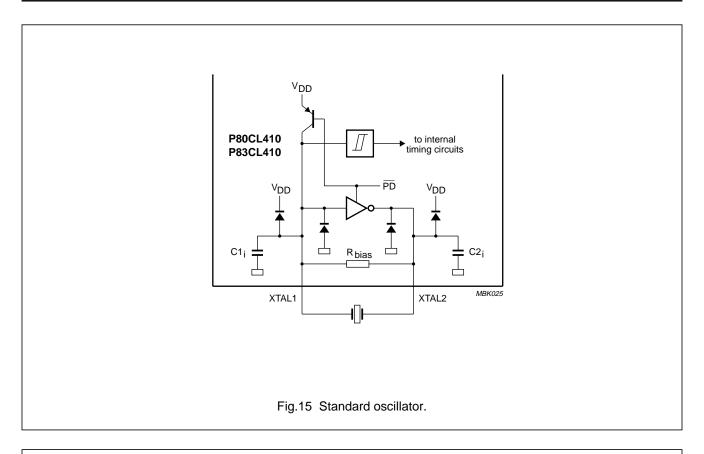

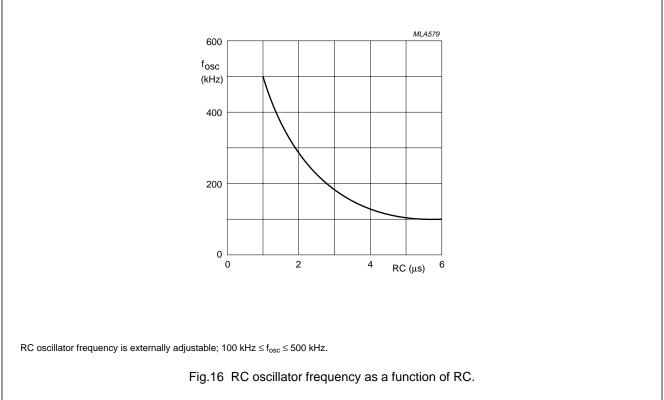

- On-chip oscillator suitable for RC, LC, quartz crystal or ceramic resonator

- Thirteen source, thirteen vector, nested interrupt structure with two priority levels

- I<sup>2</sup>C-bus interface for serial transfer on two lines

- · Enhanced architecture with:

- non-page oriented instructions

- direct addressing

- four 8-byte RAM register banks

- stack depth limited only by available internal RAM (maximum 128 bytes)

- multiply, divide, subtract and compare instructions

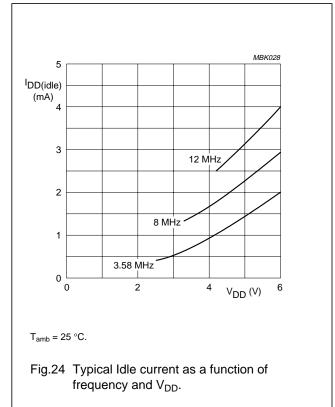

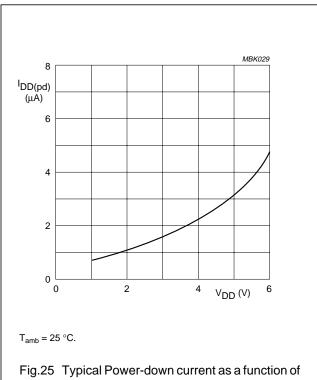

- Reduced power consumption through Power-down and Idle modes

- Wake-up via external interrupts at Port 1

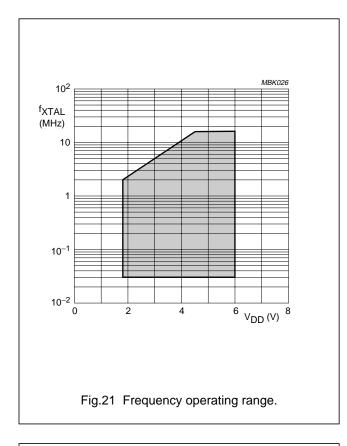

- Frequency range: DC to 12 MHz

- Supply voltage: 1.8 to 6.0 V

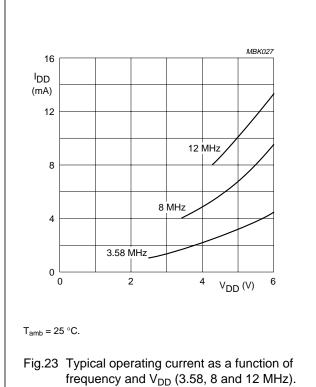

- · Very low current consumption

- Operating ambient temperature range: -40 to +85 °C.

#### 2 GENERAL DESCRIPTION

The P80CL410; P83CL410 (hereafter generally referred to as the P8xCL410) is manufactured in an advanced CMOS technology that allows the device to operate at voltages down to 1.8 V and at frequencies down to DC.

The P8xCL410 has the same instruction set as the 80C51.

The P8xCL410 features 4 kbyte ROM (83CL410), 128 bytes RAM (both ROM and RAM are externally expandable to 64 kbytes), four 8-bit ports, two 16-bit timer/counter, an I<sup>2</sup>C serial interface, a thirteen source two priority level nested interrupt structure, and on-chip oscillator circuitry suitable for quartz crystal, ceramic resonator, RC, or LC. The device operates over a wide range of supply voltages and has low power consumption.

The 8xCL410 has two reduced power modes that are the same as those on the standard 80C51.

The special reduced power feature of this device is that it can be stopped and then restarted. Running from an external clock source, the clock can be stopped and after a period of time restarted. The 8xCL410 will resume operation from where it was when the code stopped with no loss of internal state, RAM contents, or Special Function Register contents.

If the internal oscillator is used the device cannot be stopped and started, but the Power-down mode can be used to achieve similar power savings, without loss of on-chip RAM and Special Function Register values. The Power-down mode can be terminated via an interrupt.

This data sheet details the specific properties of the P80CL410; P83CL410. For details of the 80C51 core see "Data Handbook IC20".

For emulation purposes, the P85CL000 (piggy-back version) with 256 bytes of RAM is recommended. Details are given in Chapter 22.

#### 2.1 ROMless version: P80CL410

The P80CL410 is the ROMless version of the P83CL410. The mask options on the P80CL410 are fixed as follows:

- All ports have option '1S' (standard port, HIGH after reset), except ports P1.6 and P1.7 which have option '2S' (open-drain, HIGH after reset)

- Oscillator option: Oscillator 3

- · Power-on-reset option: OFF.

#### 3 APPLICATIONS

The P8xCL410 is an 8-bit general purpose microcontroller especially suited for battery-powered applications. The P8xCL410 also functions as an arithmetic processor having facilities for both binary and BCD arithmetic plus bit-handling capabilities.

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### 4 ORDERING INFORMATION

| TYPE N        | JMBER <sup>(1)</sup> | PACKAGE |                                                                                              |          |  |  |

|---------------|----------------------|---------|----------------------------------------------------------------------------------------------|----------|--|--|

| ROMIess ROM N |                      |         | DESCRIPTION                                                                                  | VERSION  |  |  |

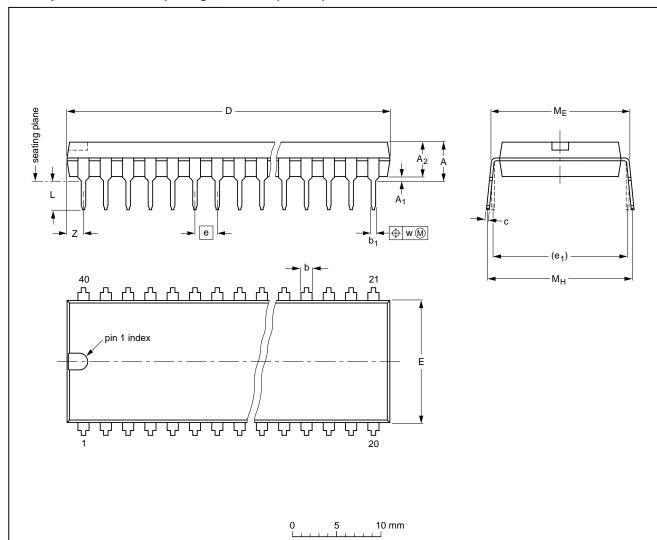

| P80CL410HFP   | P83CL410HFP          | DIP40   | plastic dual in-line package; 40 leads (600 mil)                                             | SOT129-1 |  |  |

| P80CL410HFT   | P83CL410HFT          | VSO40   | plastic very small outline package; 40 leads                                                 | SOT158-1 |  |  |

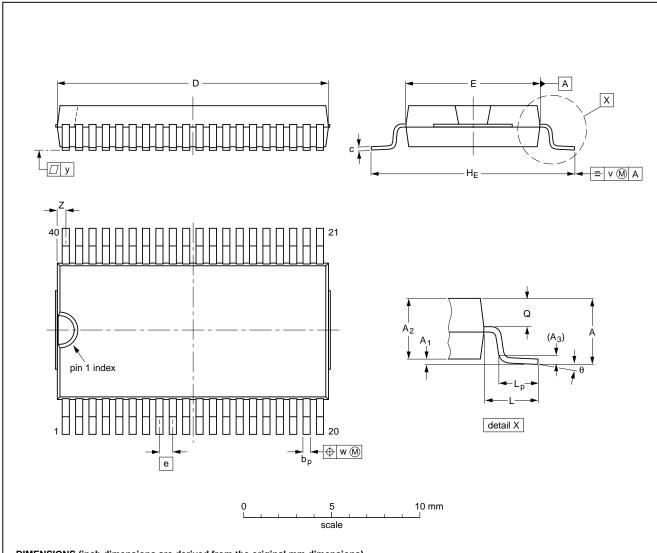

| _             | P83CL410HFH          | QFP44   | plastic quad flat package; 44 leads (lead length 1.3 mm); body $10 \times 10 \times 1.75$ mm | SOT307-2 |  |  |

### Note

1. Refer to the Order Entry Form (OEF) for this device for the full type number, including options/program.

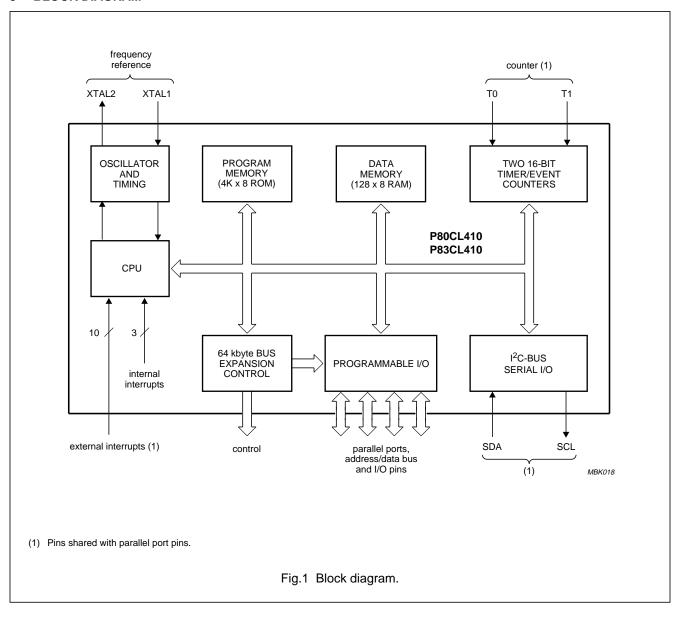

### 5 BLOCK DIAGRAM

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

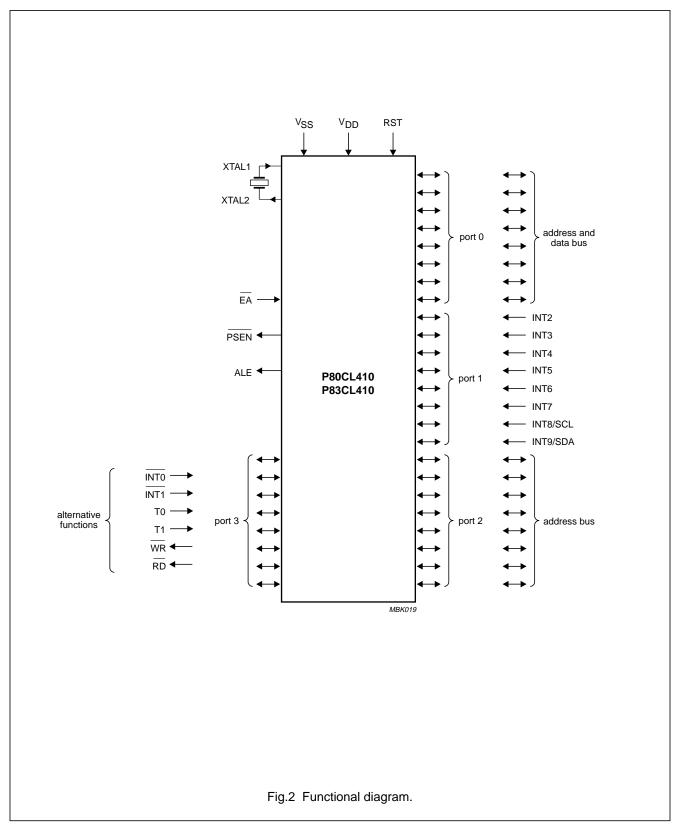

### **6 FUNCTIONAL DIAGRAM**

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

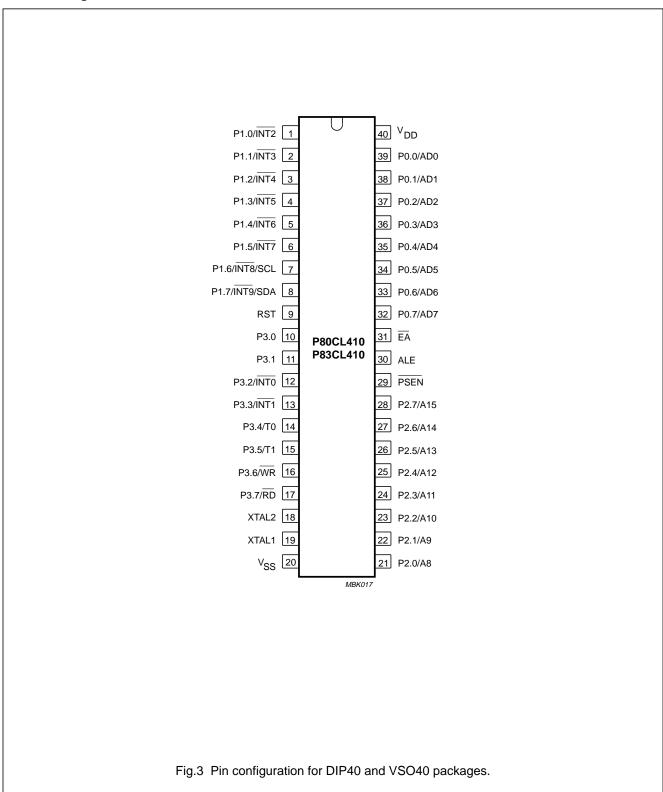

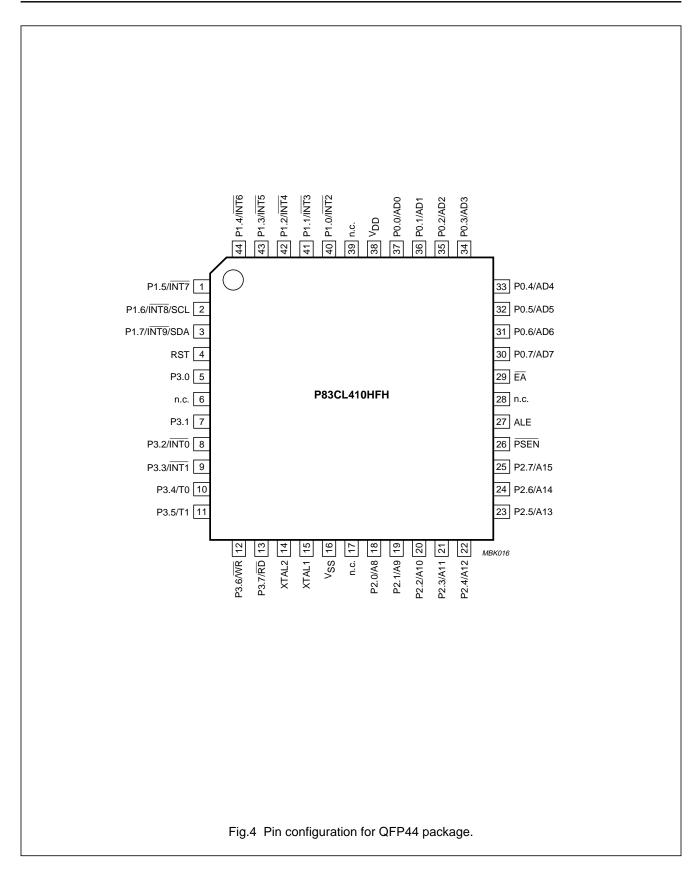

### 7 PINNING INFORMATION

### 7.1 Pinning

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### 7.2 Pin description

**Table 1** Pin description for DIP40 (SOT190-1), VSO40 (SOT319-2) and QFP44 (SOT307-2) packages For more extensive description of the port pins see Chapter 10 "I/O facilities".

|                           | DIP40<br>VSO40 QFP44 |          |                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|---------------------------|----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYMBOL                    |                      |          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| P1.0/INT2                 | 1                    | 40       | Port 1: 8-bit bidirectional I/O port (P1.0 to P1.7). Port pins that have                                                                                                                                                                                                                                                                                                                           |  |  |  |

| P1.1/INT3                 | 2                    | 41       | logic 1s written to them are pulled HIGH by internal pull-ups, and in this                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P1.2/INT4                 | 3                    | 42       | state can be used as inputs. As inputs, Port 1 pins that are externally pulled LOW will source current (In see Chapter 20) due to the internal                                                                                                                                                                                                                                                     |  |  |  |

| P1.3/INT5                 | 4                    | 43       | pulled LOW will source current (I <sub>IL</sub> , see Chapter 20) due to the internated pull-ups. Port 1 output buffers can sink/source 4 LS TTL loads.                                                                                                                                                                                                                                            |  |  |  |

| P1.5/INT®                 | 6                    | 414      | Alternative functions:                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| P1.6/INT8/SCL             | 7                    | 2        | INT2 to INT9 are external interrupt inputs                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P1.7/INT9/SDA             | 8                    | 3        | <ul> <li>SCL and SDA are the I<sup>2</sup>C-bus clock and data lines.</li> </ul>                                                                                                                                                                                                                                                                                                                   |  |  |  |

| RST                       | 9                    | 4        | <b>Reset</b> : a HIGH level on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                                                                                                                                                                                                  |  |  |  |

| P3.0                      | 10                   | 5        | Port 3: 8-bit bidirectional I/O port (P3.0 to P3.7).                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| P3.1                      | 11                   | 7        | Same characteristics as Port 1.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| P3.2/INT0                 | 12                   | 8        | Alternative functions:                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| P3.3/INT1                 | 13                   | 9        | <ul> <li>INT0 and INT1 are external interrupts 0 and 1</li> </ul>                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P3.4/T0                   | 14                   | 10       | <ul> <li>T0 and T1 are external inputs for timers 0 and 1</li> </ul>                                                                                                                                                                                                                                                                                                                               |  |  |  |

| P3.5/T1                   | 15                   | 11       | <ul> <li>WR is the external Data Memory write strobe</li> </ul>                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| P3.6/WR                   | 16                   | 12       | <ul> <li>RD is the external Data Memory read strobe.</li> </ul>                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| P3.7/RD                   | 17                   | 13       |                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| XTAL2                     | 18                   | 14       | <b>Crystal oscillator output</b> : output of the inverting amplifier of the oscillator. Left open when external clock is used.                                                                                                                                                                                                                                                                     |  |  |  |

| XTAL1                     | 19                   | 15       | <b>Crystal oscillator input</b> : input to the inverting amplifier of the oscillator, also the input for an externally generated clock source.                                                                                                                                                                                                                                                     |  |  |  |

| V <sub>SS</sub>           | 20                   | 16       | Ground: circuit ground potential.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P2.0 to P2.7<br>A8 to A15 | 21 to 28             | 18 to 25 | Port 2: 8-bit bidirectional I/O port (P2.0 to P2.7) with internal pull-ups.     Same characteristics as Port 1.                                                                                                                                                                                                                                                                                    |  |  |  |

|                           |                      |          | High-order addressing: Port 2 emits the high-order address byte     (A8 to A15) during accesses to external memory that use 16-bit     addresses (MOVX @DPTR). In this application it uses the strong internal     pull-ups when emitting logic 1s. During accesses to external memory that     use 8-bit addresses (MOVX @Ri), Port 2 emits the contents of the P2     Special Function Register. |  |  |  |

| PSEN                      | 29                   | 26       | Program Store Enable. Output read strobe to external Program Memory. When executing code out of external Program Memory, PSEN is activate twice each machine cycle. However, during each access to external Data Memory two PSEN activations are skipped.                                                                                                                                          |  |  |  |

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

|                            | PIN            |                     |                                                                                                                                                                                                                                                                                             |  |  |  |  |

|----------------------------|----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SYMBOL                     | DIP40<br>VSO40 | QFP44               | DESCRIPTION                                                                                                                                                                                                                                                                                 |  |  |  |  |

| ALE                        | 30             | 27                  | <b>Address Latch Enable</b> . Output pulse for latching the low byte of the address during access to external memory. ALE is emitted at a constant rate of $^{1}/_{6} \times f_{osc}$ , and may be used for external timing or clocking purposes (assuming MOVX instructions are not used). |  |  |  |  |

| ĒĀ                         | 31             | 29                  | External Access. When $\overline{EA}$ is held HIGH the CPU executes out of internal program memory (unless the program counter exceeds 0FFFH). Holding $\overline{EA}$ LOW forces the CPU to execute out of external memory regardless of the value of the program counter.                 |  |  |  |  |

| P0.0 to P0.7<br>AD0 to AD7 | 39 to 32       | 30 to 37            | Port 0: 8-bit open-drain bidirectional I/O port. As an open-drain output port it can sink 8 LS TTL loads. Port 0 pins that have logic 1s written to them float, and in that state will function as high impedance inputs.                                                                   |  |  |  |  |

|                            |                |                     | Low-order addressing: Port 0 is also the multiplexed low-order address and data bus during access to external memory. The strong internal pull-ups are used while emitting logic 1s within the low order address.                                                                           |  |  |  |  |

| $V_{DD}$                   | 40             | 38                  | Power supply.                                                                                                                                                                                                                                                                               |  |  |  |  |

| n.c.                       | -              | 6, 17, 28<br>and 39 | Not connected.                                                                                                                                                                                                                                                                              |  |  |  |  |

9

### Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

#### 8 FUNCTIONAL DESCRIPTION OVERVIEW

This chapter gives a brief overview of the device. The detailed functional description is in the following chapters:

Chapter 9 "Memory organization"

Chapter 10 "I/O facilities"

Chapter 11 "Timers/event counters"

Chapter 12 "Reduced power modes"

Chapter 13 "I2C-bus serial I/O"

Chapter 14 "Interrupt system"

Chapter 15 "Oscillator circuitry"

Chapter 16 "Reset".

#### 8.1 General

The P8xCL410 is a stand-alone high-performance CMOS microcontroller designed for use in real-time applications such as instrumentation, industrial control, intelligent computer peripherals and consumer products.

The device provides hardware features, architectural enhancements and new instructions to function as a controller for applications requiring up to 64 kbytes of Program Memory and/or up to 64 kbytes of Data Memory.

The P8xCL410 contains a 4 kbytes Program Memory (ROM; P83CL410); a static 128 bytes Data Memory (RAM); 32 I/O lines; two16-bit timer/event counters; a thirteen-source, two priority-level, nested interrupt structure and on-chip oscillator and timing circuit. An I<sup>2</sup>C-bus serial interface is also provided.

The device has two software-selectable modes of reduced activity for power reduction:

- **Idle mode**; freezes the CPU while allowing the timers, serial I/O and interrupt system to continue functioning.

- Power-down mode; saves the RAM contents but freezes the oscillator causing all other chip functions to be inoperative.

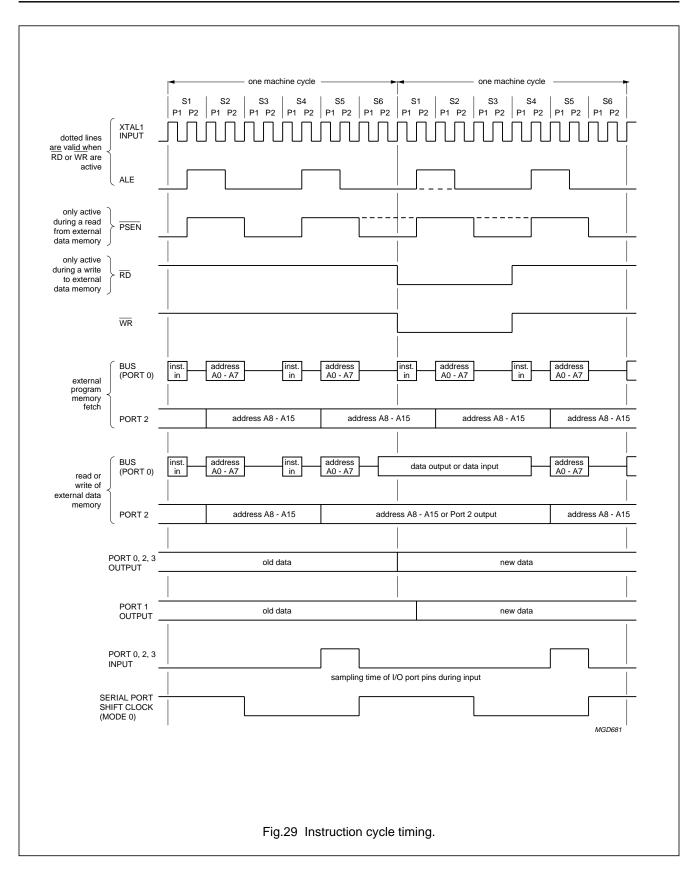

### 8.2 CPU timing

A machine cycle consists of a sequence of 6 states. Each state lasts for two oscillator periods, thus a machine cycle takes 12 oscillator periods or 1  $\mu s$  if the oscillator frequency (f<sub>osc</sub>) is 12 MHz.

#### 9 MEMORY ORGANIZATION

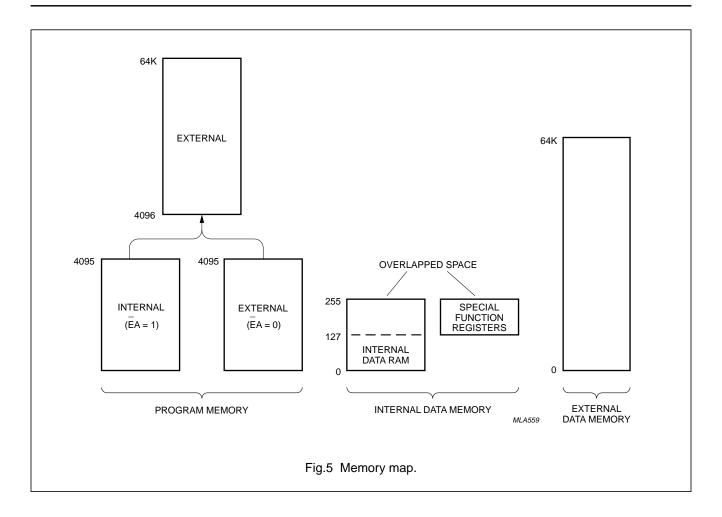

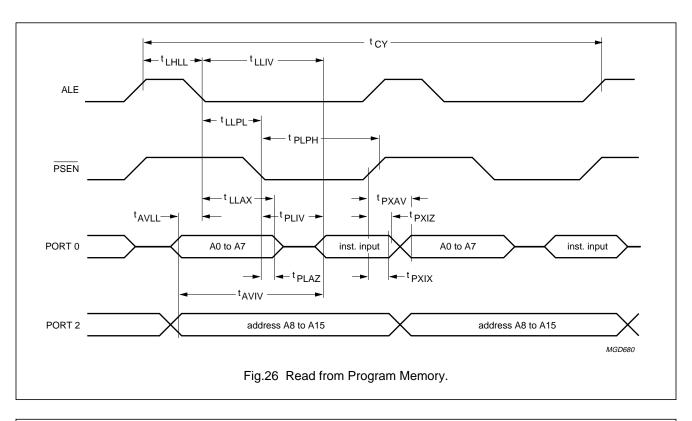

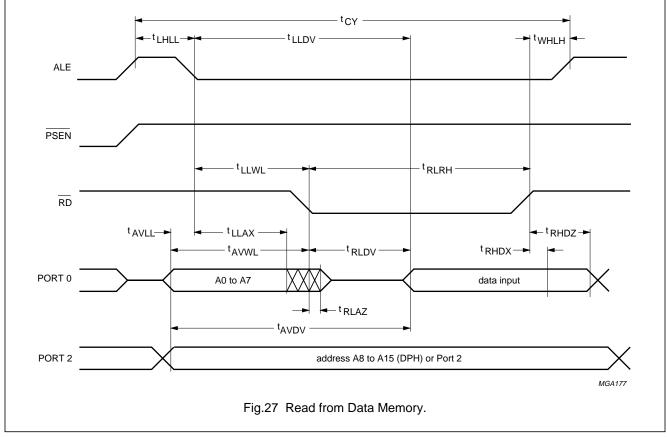

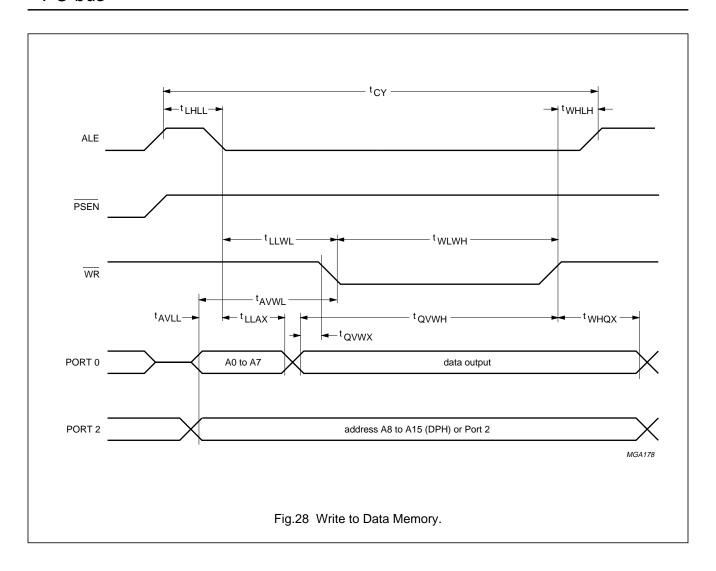

The P8xCL410 has 4 kbytes of Program Memory (ROM; P83CL410 only) plus 128 bytes of Data Memory (RAM) on board. The device has separate address spaces for Program and Data Memory (see Fig.5). Using Port latches P0 and P2, the P8xCL410 can address a maximum of 64 kbytes of program memory and a maximum of 64 kbytes of data memory. The CPU generates. The CPU generates both read  $(\overline{RD})$  and write  $(\overline{WR})$  signals for external Data Memory accesses, and the read strobe  $(\overline{PSEN})$  for external Program Memory.

### 9.1 Program Memory

After reset the CPU begins program execution at location 0000H. The lower 4 kbytes of Program Memory can be implemented in the on-chip ROM (P83CL410 only) or in external Program Memory.

If the  $\overline{\text{EA}}$  pin is tied to V<sub>DD</sub>, then Program Memory fetches from addresses 0000H to 0FFFH are directed to the internal ROM. Fetches from addresses 1000H to FFFFH are directed to external ROM. Program Counter values greater than 0FFFH are automatically addressed to external memory regardless of the state of the  $\overline{\text{EA}}$  pin.

### 9.2 Data Memory

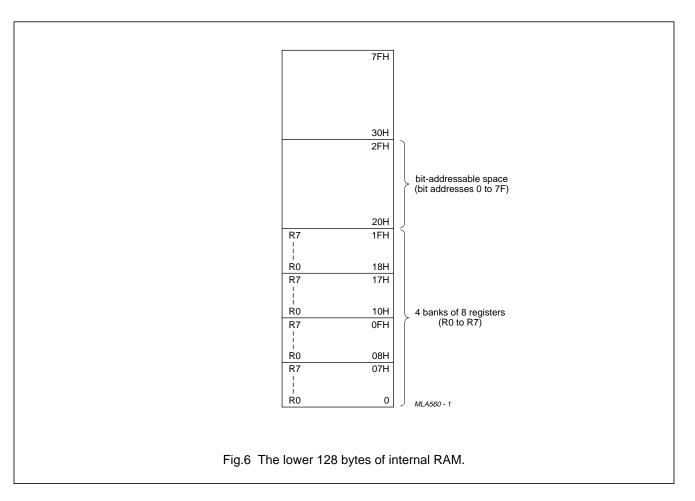

The P8xCL410 contains128 bytes of internal RAM and 27 Special Function Registers (SFR). The memory map (Fig.5) shows the internal Data Memory space divided into the lower 128, the upper 128, and the SFR space. The lower 128 bytes of the internal RAM are organized as mapped in Fig.6. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions refer to these registers within a register bank as R0 through R7. Two bits in the Program Status Word select which register bank is in use. The next 16 bytes above the register banks form a block of bit-addressable memory space. The 128 bits in this area can be directly addressed by the single-bit manipulation instructions. The remaining registers (30H to 7FH) are directly and indirectly byte addressable.

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

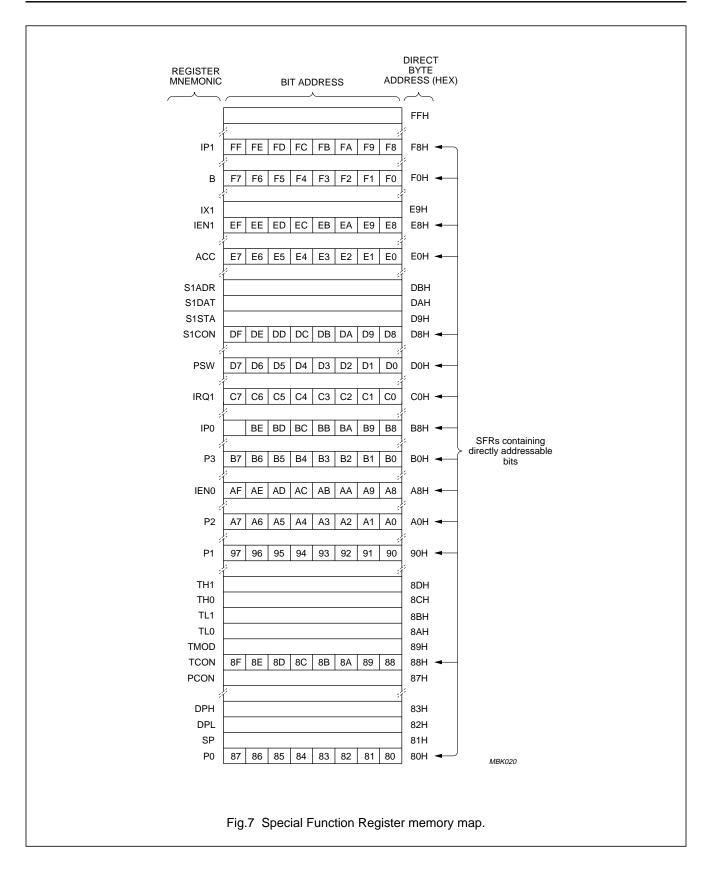

### 9.3 Special Function Registers (SFRs)

The upper 128 bytes are the address locations of the SFRs. Figure 7 shows the SFR space. The SFRs include the port latches, timers, peripheral control, serial I/O registers, etc. These registers can only be accessed by direct addressing. There are 128 directly addressable locations in the SFR address space (SFRs with addresses divisible by eight).

### 9.4 Addressing

The P8xCL410 has five methods for addressing source operands:

- Register

- Direct

- · Register-indirect

- Immediate

- Base-register plus index-register-indirect.

The first three methods can be used for addressing destination operands. Most instructions have a 'destination/source' field that specifies the data type, addressing methods and operands involved. For operations other than MOVs, the destination operand is also a source operand.

Access to memory addressing is as follows:

- Registers in one of the four register banks through register, direct or register-indirect

- Internal RAM (128 bytes) through direct or register-indirect

- Special Function Registers through direct

- External data memory through register-indirect

- Program Memory look-up tables through base-register plus index-register-indirect.

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

### P80CL410; P83CL410

#### 10 I/O FACILITIES

#### 10.1 Ports

The P8xCL410 has 32 I/O lines treated as 32 individually addressable bits or as four parallel 8-bit addressable ports. Ports 0, 1, 2 and 3 perform the alternative functions detailed below. To enable a port pin alternate function, the port bit latch in its SFR must contain a logic 1.

- Port 0 Provides the multiplexed low-order address and data bus for expanding the device with standard memories and peripherals.

- Port 1 Used for the external interrupts INT2 to INT9, and the I<sup>2</sup>C-bus interface lines SCL and SDA.

- Port 2 Provides the high-order address when expanding the device with external Program or Data Memory.

- Port 3 Pins can be configured individually to provide:

- External interrupt request inputs: INT1 and INT0

- Timer/counter inputs: T1 and T0

- Control signals to read and write to external memories: RD and WR.

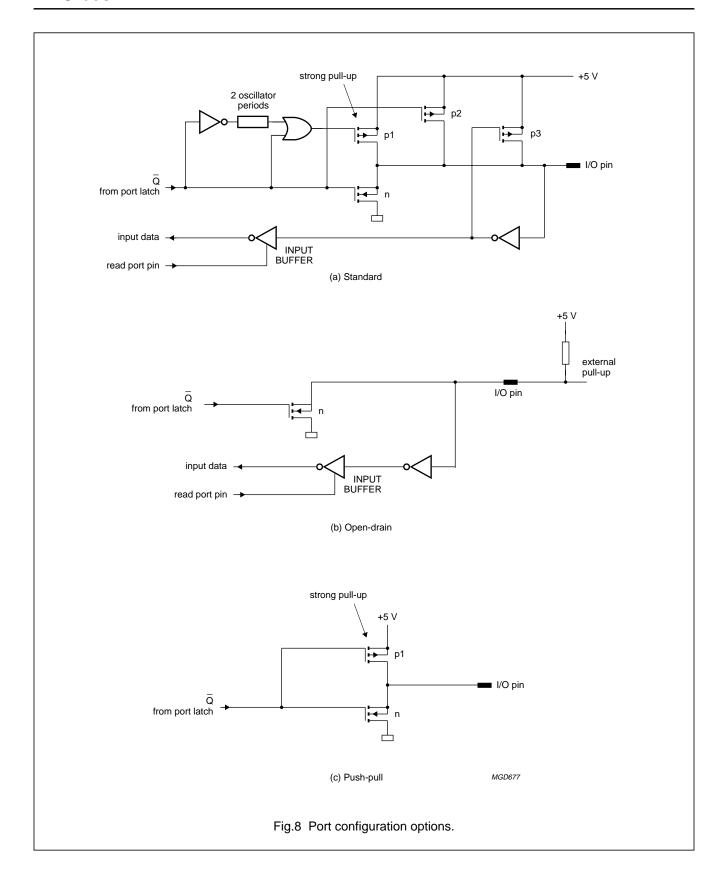

Each port consists of a latch (SFRs P0 to P3), an output driver and input buffer. Ports 1, 2, and 3 have internal pull-ups Figure 8(a) shows that the strong transistor 'p1' is turned on for only 2 oscillator periods after a LOW-to-HIGH transition in the port latch. When on, it turns on 'p3' (a weak pull-up) through the inverter. This inverter and 'p3' form a latch which holds the logic 1. In Port 0 the pull-up 'p1' is only on when emitting logic 1s for external memory access. Writing a logic 1 to a Port 0 bit latch leaves both output transistors switched off so that the pin can be used as a high-impedance input.

### 10.2 Port options

The pins of port 1 (except P1.6 and P1.7; with option 2S only), port 2 and port 3 may be individually configured with one of the following options. These options are also shown in Fig.8.

- Option 1 **Standard Port**; quasi-bidirectional I/O with pull-up. The strong booster pull-up 'p1' is turned on for two oscillator periods after a LOW-to-HIGH transition in the port latch; Fig.8(a).

- Option 2 **Open-drain**; quasi-bidirectional I/O with n-channel open-drain output. Use as an output requires the connection of an external pull-up resistor; see Fig.8(b).

Option 3 **Push-pull**; output with drive capability in both polarities. Under this option, pins can only be used as outputs; see Fig.8(c).

### 10.3 Port 0 options

The definition of port options for Port 0 is slightly different. Two cases are considered. First, access to external memory ( $\overline{EA} = 0$  or access above the built-in memory boundary) and second, I/O accesses.

### 10.3.1 EXTERNAL MEMORY ACCESSES

- Option 1 True logic 0 and logic 1 are written as address to the external memory (strong pull-up to be used).

- Option 2 An external pull-up resistor is required for external accesses.

- Option 3 Not allowed for external memory accesses as the port can only be used as output.

#### 10.3.2 I/O Accesses

- Option 1 When writing a logic 1 to the port latch, the strong pull-up 'p1' will be on for 2 oscillator periods. No weak pull-up exists. Without an external pull-up, this option can be used as a high-impedance input.

- Option 2 Open-drain; quasi-directional I/O with n-channel open-drain output. Use as an output requires the connection of an external pull-up resistor. See Fig.8(b).

- Option 3 Push-Pull; output with drive capability in both polarities. Under this option pins can only be used as outputs. See Fig.8(c).

### 10.4 SET/RESET options

Individual mask selection of the post-reset state is available with any of the above pins. The required selection is made by appending 'S' or 'R' to Options 1, 2, or 3 above.

Option R RESET, at reset this pin will be initialized LOW.

Option S SET, at reset this pin will be initialized HIGH.

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

### P80CL410; P83CL410

### Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

#### 11 TIMERS/EVENT COUNTERS

The P8xCL410 contains two16-bit timer/event counter registers; Timer 0 and Timer 1, which can perform the following functions:

- Measure time intervals and pulse durations

- · Count events

- Generate interrupt requests.

In the 'Timer' operating mode the register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is  $\frac{1}{12} \times f_{osc}$ .

In the 'Counter' operating mode, the register is incremented in response to a HIGH-to-LOW transition. Since it takes 2 machine cycles (24 oscillator periods) to recognize a HIGH-to-LOW transition, the maximum count rate is  $1/\!\!\!\!/_{24} \times f_{osc}.$  To ensure a given level is sampled, it should be held for at least one complete machine cycle.

Timer 0 and Timer 1 can be programmed independently to operate in four modes:

- Mode 0 8-bit timer or 8-bit counter each with divide-by-32 prescaler.

- Mode 1 16-bit time-interval or event counter.

- Mode 2 8-bit time-interval or event counter with automatic reload upon overflow.

- Mode 3 Timer 0 establishes TL0 and TH0 as two separate counters.

### 12 REDUCED POWER MODES

There are two software selectable modes of reduced activity for further power reduction: Idle and Power-down.

### 12.1 Idle mode

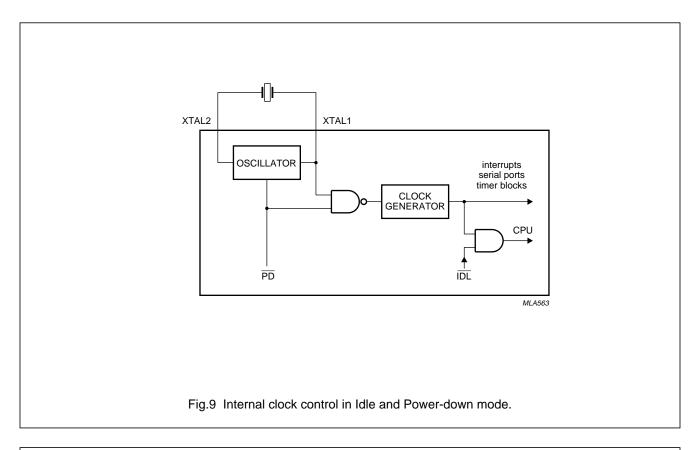

Idle mode operation permits the external interrupts,  $I^2C$ -bus, and timer blocks to continue to function while the clock to the CPU is halted.

Idle mode is entered by setting the IDL bit in the Power Control Register (PCON.0, see Table 3). The instruction that sets IDL is the last instruction executed in the normal operating mode before the Idle mode is activated

Once in Idle mode, the CPU status is preserved along with the Stack Pointer, Program Counter, Program Status Word and Accumulator. The RAM and all other registers maintain their data during Idle mode. The status of the external pins during Idle mode is shown in Table 4. The following functions remain active during the Idle mode:

- Timer 0 and Timer 1

- I<sup>2</sup>C-bus

- External interrupt.

These functions may generate an interrupt or reset; thus ending the Idle mode.

There are two ways to terminate the Idle mode:

- Activation of any enabled interrupt will cause IDL (PCON.0) to be cleared by hardware thus terminating the Idle mode. The interrupt is serviced, and following the RETI instruction, the next instruction to be executed will be the one following the instruction that put the device in the Idle mode. The flag bits GF0 (PCON.2) and GF1 (PCON.3) may be used to determine whether the interrupt was received during normal execution or during the Idle mode. For example, the instruction that writes to PCON.0 can also set or clear one or both flag bits. When the Idle mode is terminated by an interrupt, the service routine can examine the status of the flag bits.

- The second way of terminating the Idle mode is with an external hardware reset. Since the oscillator is still running, the hardware reset is required to be active for two machine cycles (24 oscillator periods) to complete the reset operation. Reset redefines all SFRs but does not affect the on-chip RAM.

### 12.2 Power-down mode

Operation in Power-down mode freezes the oscillator. The internal connections which link both Idle and Power-down signals to the clock generation circuit are shown in Fig.9.

Power-down mode is entered by setting the PD bit in the Power Control Register (PCON.1, see Table 2). The instruction that sets PD is the last executed prior to going into the Power-down mode.

Once in the Power-down mode, the oscillator is stopped. The contents of the on-chip RAM and the SFRs are preserved. The port pins output the value held by their respective SFRs. ALE and PSEN are held LOW.

In the Power-down mode,  $V_{DD}$  may be reduced to minimize circuit power consumption. The supply voltage must not be reduced until the Power-down mode is entered, and must be restored before the hardware reset is applied which will free the oscillator. Reset should not be released until the oscillator has restarted and stabilized.

### Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### 12.3 Wake-up from Power-down mode

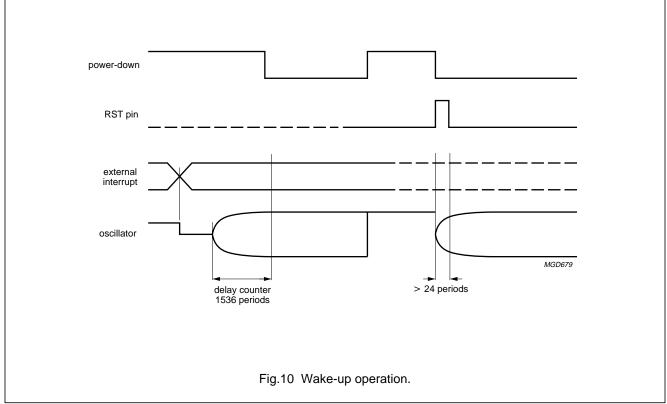

When in Power-down mode the controller can be woken-up with either the external interrupts  $\overline{\text{INT2}}$  to  $\overline{\text{INT9}}$ , or a reset operation. The wake-up operation has two basic approaches as explained in Section 12.3.1; 12.3.2 and illustrated in Fig.10.

### 12.3.1 WAKE-UP USING INT2 TO INT9

If any of the interrupts  $\overline{\text{INT2}}$  to  $\overline{\text{INT9}}$  are enabled, the device can be woken-up from the Power-down mode with the external interrupts. To ensure that the oscillator is stable before the controller restarts, the internal clock will remain inactive for 1536 oscillator periods. This is controlled by an on-chip delay counter.

#### 12.3.2 WAKE-UP USING RST

To wake-up the P8xCL410, the RST pin must be kept HIGH for a minimum of 24 periods. The on-chip delay counter is inactive. The user must ensure that the oscillator is stable before any operation is attempted.

### 12.4 Power Control Register (PCON)

See Tables 2 and 3. Idle and Power-down modes are activated by software using this SFR. PCON is not bit-addressable.

### 12.5 Status of external pins

The status of the external pins during Idle and Power-down mode is shown in Table 3. If the Power-down mode is activated whilst accessing external Program Memory, the port data that is held in the Special Function Register P2 is restored to Port 2.

If the data is a logic 1, the port pin is held HIGH during the Power-down mode by the strong pull-up transistor 'p1'; see Fig.8(a).

Table 2 Power Control Register (address 87H)

| 7 | 6 | 5 | 4 | 3   | 2   | 1  | 0   |

|---|---|---|---|-----|-----|----|-----|

| _ | _ | _ | _ | GF1 | GF0 | PD | IDL |

Table 3 Description of PCON bits

| BIT        | SYMBOL      | DESCRIPTION                                                   |  |  |  |

|------------|-------------|---------------------------------------------------------------|--|--|--|

| 7, 6, 5, 4 | _           | reserved                                                      |  |  |  |

| 3 and 2    | GF1 and GF0 | General purpose flag bits                                     |  |  |  |

| 1          | PD          | ower-down bit; setting this bit activates the Power-down mode |  |  |  |

| 0          | IDL         | Idle mode bit; setting this bit activates the Idle mode       |  |  |  |

Table 4 Status of external pins during Idle and Power-down modes

| MODE       | MEMORY   | ALE | PSEN | PORT 0    | PORT 1    | PORT 2    | PORT 3    | PORT 4    |

|------------|----------|-----|------|-----------|-----------|-----------|-----------|-----------|

| Idle       | internal | 1   | 1    | port data |

|            | external | 1   | 1    | floating  | port data | address   | port data | port data |

| Power-down | internal | 0   | 0    | port data |

|            | external | 0   | 0    | floating  | port data | port data | port data | port data |

17

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

### P80CL410; P83CL410

### Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### 13 I2C-BUS SERIAL I/O

The serial port supports the twin line I<sup>2</sup>C-bus, which consists of a serial data line (SDA) and a serial clock line (SCL). These lines also function as the I/O port lines P1.7 and P1.6 respectively.

The system is unique because data transport, clock generation, address recognition and bus control arbitration are all controlled by hardware.

The I<sup>2</sup>C-bus serial I/O has complete autonomy in byte handling and operates in 4 modes:

- Master transmitter

- Master receiver

- · Slave transmitter

- Slave receiver.

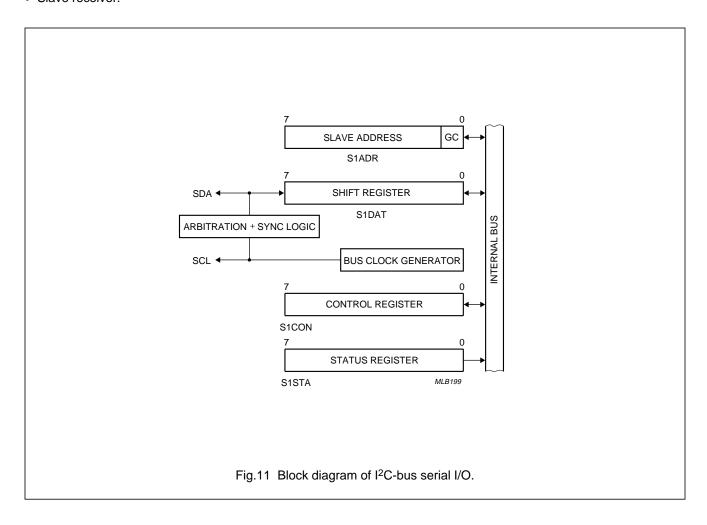

These functions are controlled by the Serial Control Register S1CON. S1STA is the Status Register whose contents may also be used as a vector to various service routines. S1DAT is the Data Shift Register and S1ADR is the Slave Address Register. Slave address recognition is performed by on-chip hardware.

Figure 11 is the block diagram of the I<sup>2</sup>C-bus serial I/O.

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### 13.1 Serial Control Register (S1CON)

Table 5

Serial Control Register (SFR address D8H)

| 7   | 6    | 5   | 4   | 3  | 2  | 1   | 0   |

|-----|------|-----|-----|----|----|-----|-----|

| CR2 | ENS1 | STA | STO | SI | AA | CR1 | CR0 |

Table 6 Description of S1CON bits

| BIT | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CR2    | This bit along with bits CR1 (S1CON.1) and CR0 (S1CON.0) determines the serial clock frequency when SIO is in the Master mode. See Table 7.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6   | ENS1   | <b>ENABLE serial I/O</b> . When ENS1 = 0, the serial I/O is disabled. SDA and SCL outputs are in the high impedance state; P1.6 and P1.7 function as open-drain ports. When ENS1 = 1, the serial I/O is enabled. Output port latches P1.6 and P1.7 must be set to logic 1.                                                                                                                                                                                                                                                                                         |

| 5   | STA    | <b>START flag</b> . When this bit is set in Slave mode, the SIO hardware checks the status of the I <sup>2</sup> C-bus and generates a START condition if the bus is free or after the bus becomes free. If STA is set while the SIO is in Master mode, SIO will generate a repeated START condition.                                                                                                                                                                                                                                                              |

| 4   | STO    | STOP flag. With this bit set while in Master mode a STOP condition is generated. When a STOP condition is detected on the I <sup>2</sup> C-bus, the SIO hardware clears the STO flag. STO may also be set in Slave mode in order to recover from an error condition. In this case no STOP condition is transmitted to the I <sup>2</sup> C-bus. However, the SIO hardware behaves as if a STOP condition has been received and releases the SDA and SCL. The SIO then switches to the not addressed slave receiver mode. The STOP flag is cleared by the hardware. |

| 3   | SI     | SIO interrupt flag. This flag is set, and an interrupt is generated, after any of the following events occur:                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |        | A START condition is generated in Master mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |        | Own slave address has been received during AA = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |        | The general call address has been received while GC (S1ADR.0) = 1 and AA = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |        | A data byte has been received or transmitted in Master mode (even if arbitration is lost)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |        | A data byte has been received or transmitted as selected slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |        | A STOP or START condition is received as selected slave receiver or transmitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2   | AA     | Assert Acknowledge. When this bit is set, an acknowledge (low level to SDA) is returned during the acknowledge clock pulse on the SCL line when:                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |        | Own slave address is received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |        | General call address is received; GC (S1ADR.0) = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |        | A data byte is received while the device is programmed to be a Master Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |        | A data byte is received while the device is a selected Slave Receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | When this bit is reset, no acknowledge is returned. Consequently, no interrupt is requested when the own slave address or general call address is received.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1   | CR1    | These two bits along with the CR2 (S1CON.7) bit determine the serial clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0   | CR0    | when SIO is in the Master mode. See Table 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

Table 7

Selection of the serial clock frequency SCL in a Master mode of operation

| CR2 | CR1 | CR0 | f DIVISOR                | BIT RATE (kHz) at f <sub>osc</sub> |       |        |  |

|-----|-----|-----|--------------------------|------------------------------------|-------|--------|--|

| GRZ |     |     | f <sub>osc</sub> DIVISOR | 3.58 MHz                           | 6 MHz | 12 MHz |  |

| 0   | 0   | 0   | 256                      | 14.0                               | 23.4  | 46.9   |  |

| 0   | 0   | 1   | 224                      | 16.0                               | 26.8  | 53.6   |  |

| 0   | 1   | 0   | 192                      | 18.6                               | 31.3  | 62.5   |  |

| 0   | 1   | 1   | 160                      | 22.4                               | 37.5  | 75.0   |  |

| 1   | 0   | 0   | 960                      | 3.73                               | 6.25  | 12.5   |  |

| 1   | 0   | 1   | 120                      | 29.8                               | 50.0  | 100.0  |  |

| 1   | 1   | 0   | 60                       | 59.7                               | 100.0 | _      |  |

| 1   | 1   | 1   | not allowed              | _                                  | _     | _      |  |

### 13.2 Serial Status Register (S1STA)

S1STA is a read-only register. The contents of this register may be used as a vector to a service routine. This optimizes the response time of the software and consequently that of the  $I^2C$ -bus. The status codes for all possible modes of the  $I^2C$ -bus interface are given in Tables 10 to 14.

Table 8 Serial Status Register (address D9H)

| 7   | 6   | 5   | 4   | 3   | 2 | 1 | 0 |  |

|-----|-----|-----|-----|-----|---|---|---|--|

| SC4 | SC3 | SC2 | SC1 | SC0 | 0 | 0 | 0 |  |

Table 9 Description of S1STA bits

| BIT    | SYMBOL     | DESCRIPTION                      |  |  |  |

|--------|------------|----------------------------------|--|--|--|

| 3 to 7 | SC4 to SC0 | 5-bit status code                |  |  |  |

| 0 to 2 | _          | these three bits are always zero |  |  |  |

### Table 10 MST/TRX mode

| S1STA VALUE | DESCRIPTION                                            |

|-------------|--------------------------------------------------------|

| 08H         | a START condition has been transmitted                 |

| 10H         | a repeated START condition has been transmitted        |

| 18H         | SLA and W have been transmitted, ACK has been received |

| 20H         | SLA and W have been transmitted, ACK received          |

| 28H         | DATA of S1DAT has been transmitted, ACK received       |

| 30H         | DATA of S1DAT has been transmitted, ACK received       |

| 38H         | arbitration lost in SLA, R/W or DATA                   |

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### Table 11 MST/REC mode

| S1STA VALUE | DESCRIPTION                                     |

|-------------|-------------------------------------------------|

| 08H         | a START condition has been transmitted          |

| 10H         | a repeated START condition has been transmitted |

| 38H         | arbitration lost while returning ACK            |

| 40H         | SLA and R have been transmitted, ACK received   |

| 48H         | SLA and R have been transmitted, ACK received   |

| 50H         | DATA has been received, ACK returned            |

| 58H         | DATA has been received, ACK returned            |

### Table 12 SLV/REC mode

| S1STA VALUE | DESCRIPTION                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------|

| 60H         | own SLA and W have been received, ACK returned                                                             |

| 68H         | arbitration lost in SLA, R/W as MST. Own SLA and W have been received, ACK returned                        |

| 70H         | general CALL has been received, ACK returned                                                               |

| 78H         | arbitration lost in SLA, R/W as MST; general CALL has been received                                        |

| 80H         | previously addressed with own SLA; DATA byte received, ACK returned                                        |

| 88H         | previously addressed with own SLA; DATA byte received, ACK returned                                        |

| 90H         | previously addressed with general CALL; DATA byte has been received, ACK has been returned                 |

| 98H         | previously addressed with general CALL; DATA byte has been received, ACK has been returned                 |

| АОН         | a STOP condition or repeated START condition has been received while still addressed as SLV/REC or SLV/TRX |

### Table 13 SLV/TRX mode

| S1STA VALUE | DESCRIPTION                                                                         |

|-------------|-------------------------------------------------------------------------------------|

| A8H         | own SLA and R have been received, ACK returned                                      |

| В0Н         | arbitration lost in SLA, R/W as MST; own SLA and R have been received, ACK returned |

| B8H         | DATA byte has been transmitted, ACK received                                        |

| C0H         | DATA byte has been transmitted, ACK received                                        |

| C8H         | last DATA byte has been transmitted (AA = 0), ACK received                          |

### Table 14 Miscellaneous

| S1STA VALUE | DESCRIPTION                                                                                 |

|-------------|---------------------------------------------------------------------------------------------|

| 00H         | bus error during MST mode or selected SLV mode, due to an erroneous START or STOP condition |

| F8H         | no relevant state information available, SI = 0                                             |

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

Table 15 Symbols used in Tables 10 to 14

| SYMBOL | DESCRIPTION                                     |

|--------|-------------------------------------------------|

| SLA    | 7-bit slave address                             |

| R      | read bit                                        |

| W      | write bit                                       |

| ACK    | acknowledgement (acknowledge bit is logic 0)    |

| ACK    | no acknowledgement (acknowledge bit is logic 1) |

| DATA   | 8-bit data byte to or from I <sup>2</sup> C-bus |

| MST    | master                                          |

| SLV    | slave                                           |

| TRX    | transmitter                                     |

| REC    | receiver                                        |

### 13.3 Data Shift Register (S1DAT)

S1DAT contains the serial data to be transmitted or data which has just been received. The MSB (bit 7) is transmitted or received first; i.e. data shifted from right to left.

Table 16 Data Shift Register (SFR address DAH)

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|---------|---------|---------|---------|

| S1DAT.7 | S1DAT.6 | S1DAT.5 | S1DAT.4 | S1DAT.3 | S1DAT.2 | S1DAT.1 | S1DAT.0 |

### 13.4 Address Register (S1ADR)

This 8-bit register may be loaded with the 7-bit slave address to which the controller will respond when programmed as a slave receiver/transmitter.

Table 17 Address Register (SFR address DBH)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0  |

|------|------|------|------|------|------|------|----|

| SLA6 | SLA5 | SLA4 | SLA3 | SLA2 | SLA1 | SLA0 | GC |

Table 18 Description of S1ADR bits

| BIT    | SYMBOL       | DESCRIPTION                                                                                                                                                                                |

|--------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 1 | SLA6 to SLA0 | own slave address                                                                                                                                                                          |

| 0      |              | this bit is used to determine whether the general call address is recognized; when GC = 0, the general call address is not recognized; when GC = 1, the general call address is recognized |

### Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

#### 14 INTERRUPT SYSTEM

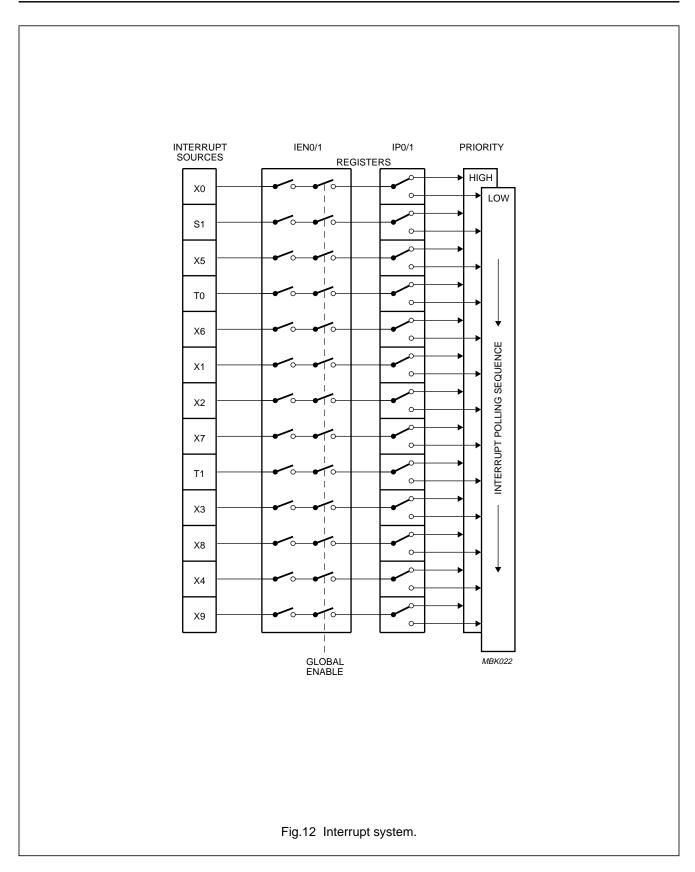

External events and the real-time-driven on-chip peripherals require service by the CPU at unpredictable times. To tie the asynchronous activities of these functions to normal program execution a multiple-source, two-priority-level, nested interrupt system is provided. The system is shown in Fig.12. The P8xCL410 acknowledges interrupt requests from thirteen sources as follows:

- INTO and INT1

- Timer 0 and Timer 1

- I2C-bus

- INT2 to INT9.

Each interrupt vectors to a separate location in Program Memory for its service routine. Each source can be individually enabled or disabled by corresponding bits in the Interrupt Enable Registers (IEN0 and IEN1). The priority level is selected via the Interrupt Priority Registers (IP0 and IP1). All enabled sources can be globally disabled or enabled. Figure 12 shows the interrupt system.

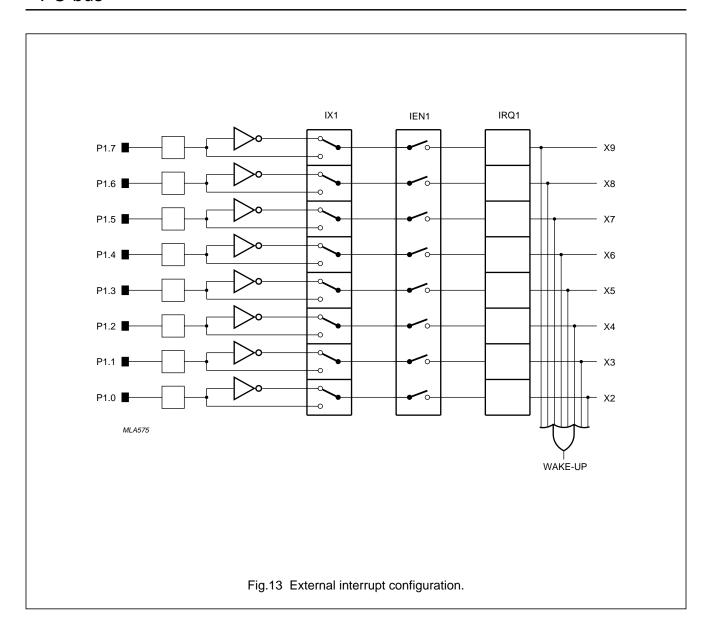

### 14.1 External interrupts INT2 to INT9

Port 1 lines serve an alternative purpose as eight additional interrupts INT2 to INT9. When enabled, each of these lines may wake-up the device from the Power-down mode. Using the Interrupt Polarity Register (IX1), each pin may be initialized to be either active HIGH or active LOW. IRQ1 is the Interrupt Request Flag Register. If the interrupt is enabled, each flag will be set on an interrupt request but must be cleared by software, i.e. via the interrupt software or when the interrupt is disabled.

Port 1 interrupts are level sensitive. A Port 1 interrupt will be recognized when a level (HIGH or LOW depending on the Interrupt Polarity Register) on P1.n is held active for at least one machine cycle. The interrupt request is not serviced until the next machine cycle. Figure 13 shows the external interrupt configuration.

### 14.2 Interrupt priority

Each interrupt source can be set to either a high priority or to a low priority. If a low priority interrupt is received simultaneously with a high priority interrupt, the high priority interrupt will be dealt with first.

If interrupts of the same priority are requested simultaneously, the processor will branch to the interrupt polled first, according to the sequence shown in Table 19 and in Fig.12. The 'vector address' is the ROM location where the appropriate interrupt service routine starts.

Table 19 Interrupt vector polling sequence

| SYMBOL     | VECTOR<br>ADDRESS (HEX) | SOURCE                |  |

|------------|-------------------------|-----------------------|--|

| X0 (first) | 0003                    | External 0            |  |

| S1         | 002B                    | I <sup>2</sup> C port |  |

| X5         | 0053                    | External 5            |  |

| T0         | 000B                    | Timer 0               |  |

| X6         | 005B                    | External 6            |  |

| X1         | 0013                    | External 1            |  |

| X2         | 003B                    | External 2            |  |

| X7         | 0063                    | External 7            |  |

| T1         | 001B                    | Timer 1               |  |

| Х3         | 0043                    | External 3            |  |

| X8         | 006B                    | External 8            |  |

| X4         | 004B                    | External 4            |  |

| X9 (last)  | xt0073                  | External 9            |  |

A low priority interrupt routine can only be interrupted by a high priority interrupt. A high priority interrupt routine cannot be interrupted.

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### 14.3 Interrupt registers

The registers used in the interrupt system are listed in Table 20. Tables 21 to 32 describe the contents of these registers.

Table 20 Special Function Registers related to the interrupt system

| ADDRESS | REGISTER | DESCRIPTION                                |  |  |  |

|---------|----------|--------------------------------------------|--|--|--|

| A8H     | IEN0     | Interrupt Enable Register                  |  |  |  |

| E8H     | IEN1     | Interrupt Enable Register (INT2 to INT9)   |  |  |  |

| B8H     | IP0      | Interrupt Priority Register                |  |  |  |

| F8H     | IP1      | Interrupt Priority Register (INT2 to INT9) |  |  |  |

| E9H     | IX1      | Interrupt Polarity Register                |  |  |  |

| C0H     | IRQ1     | Interrupt Request Flag Register            |  |  |  |

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### 14.3.1 INTERRUPT ENABLE REGISTER (IEN0)

Bit values: 0 = interrupt disabled; 1 = interrupt enabled.

Table 21 Interrupt Enable Register (SFR address A8H)

| 7  | 6 | 5   | 4 | 3   | 2   | 1   | 0   |

|----|---|-----|---|-----|-----|-----|-----|

| EA | _ | ES1 | _ | ET1 | EX1 | ET0 | EX0 |

Table 22 Description of IEN0 bits

| BIT | SYMBOL | DESCRIPTION                                                                                                                        |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA     | general enable/disable control. If EA = 0, no interrupt is enabled. If EA = 1, any individually enabled interrupt will be accepted |

| 6   | _      | reserved                                                                                                                           |

| 5   | ES1    | enable I <sup>2</sup> C-bus SIO interrupt                                                                                          |

| 4   | _      | reserved                                                                                                                           |

| 3   | ET1    | enable Timer 1 interrupt (T1)                                                                                                      |

| 2   | EX1    | enable external interrupt 1                                                                                                        |

| 1   | ET0    | enable Timer 0 interrupt (T0)                                                                                                      |

| 0   | EX0    | enable external interrupt 0                                                                                                        |

### 14.3.2 INTERRUPT ENABLE REGISTER (IEN1)

Bit values: 0 = interrupt disabled; 1 = interrupt enabled.

Table 23 Interrupt Enable Register (SFR address E8H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| EX9 | EX8 | EX7 | EX6 | EX5 | EX4 | EX3 | EX2 |

Table 24 Description of IEN1 bits

| BIT | SYMBOL | DESCRIPTION                 |

|-----|--------|-----------------------------|

| 7   | EX9    | enable external interrupt 9 |

| 6   | EX8    | enable external interrupt 8 |

| 5   | EX7    | enable external interrupt 7 |

| 4   | EX7    | enable external interrupt 6 |

| 3   | EX5    | enable external interrupt 5 |

| 2   | EX4    | enable external interrupt 4 |

| 1   | EX3    | enable external interrupt 3 |

| 0   | EX2    | enable external interrupt 2 |

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

14.3.3 INTERRUPT PRIORITY REGISTER (IP0)

Bit values: 0 = low priority; 1 = high priority.

Table 25 Interrupt Priority Register (SFR address B8H)

| 7 | 6 | 5   | 4 | 3   | 2   | 1   | 0   |

|---|---|-----|---|-----|-----|-----|-----|

| _ | _ | PS1 | _ | PT1 | PX1 | PT0 | PX0 |

Table 26 Description of IP0 bits

| BIT | SYMBOL | DESCRIPTION                                       |

|-----|--------|---------------------------------------------------|

| 7   | -      | reserved                                          |

| 6   | _      | reserved                                          |

| 5   | PS1    | I <sup>2</sup> C-bus SIO interrupt priority level |

| 4   | _      | reserved                                          |

| 3   | PT1    | Timer 1 interrupt priority level                  |

| 2   | PX1    | external interrupt 1 priority level               |

| 1   | PT0    | Timer 0 interrupt priority level                  |

| 0   | PX0    | external interrupt 0 priority level               |

14.3.4 INTERRUPT PRIORITY REGISTER (IP1)

Bit values: 0 = low priority; 1 = high priority.

Table 27 Interrupt Priority Register (SFR address F8H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| PX9 | PX8 | PX7 | PX6 | PX5 | PX4 | PX3 | PX2 |

Table 28 Description of IP1 bits

| BIT | SYMBOL | DESCRIPTION                         |

|-----|--------|-------------------------------------|

| 7   | PX9    | external interrupt 9 priority level |

| 6   | PX8    | external interrupt 8 priority level |

| 5   | PX7    | external interrupt 7 priority level |

| 4   | PX6    | external interrupt 6 priority level |

| 3   | PX5    | external interrupt 5 priority level |

| 2   | PX4    | external interrupt 4 priority level |

| 1   | PX3    | external interrupt 3 priority level |

| 0   | PX2    | external interrupt 2 priority level |

28

# Low voltage 8-bit microcontrollers with I<sup>2</sup>C-bus

P80CL410; P83CL410

### 14.3.5 INTERRUPT POLARITY REGISTER (IX1)

Writing either a logic 1 or logic 0 to any Interrupt Polarity Register bit sets the polarity level of the corresponding external interrupt to an active HIGH or active LOW respectively.

Table 29 Interrupt Polarity Register (SFR address E9H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IL9 | IL8 | IL7 | IL6 | IL5 | IL4 | IL3 | IL2 |

### Table 30 Description of IX1 bits

| BIT | SYMBOL | DESCRIPTION                         |

|-----|--------|-------------------------------------|

| 7   | IL9    | external interrupt 9 polarity level |

| 6   | IL8    | external interrupt 8 polarity level |

| 5   | IL7    | external interrupt 7 polarity level |

| 4   | IL6    | external interrupt 6 polarity level |

| 3   | IL5    | external interrupt 5 polarity level |

| 2   | IL4    | external interrupt 4 polarity level |

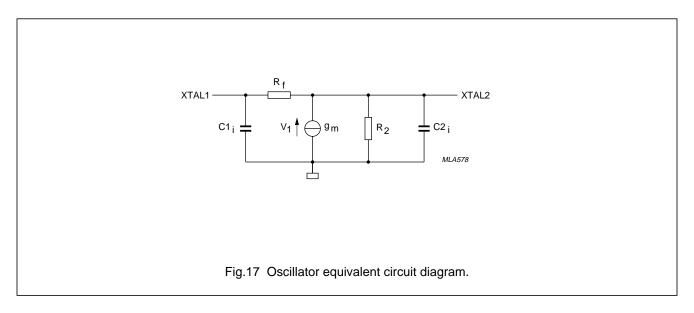

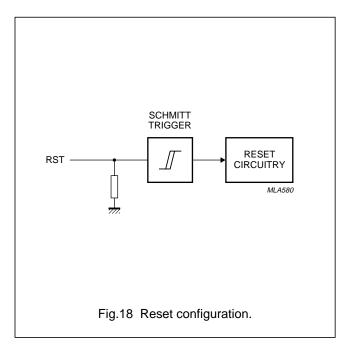

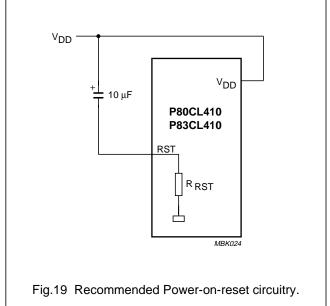

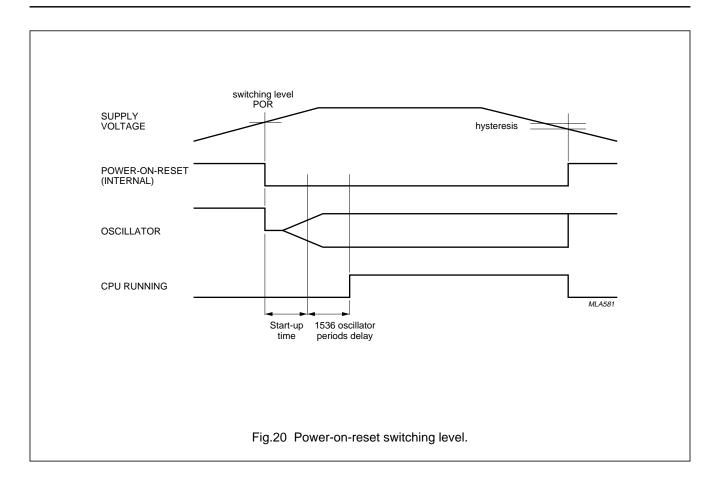

| 1   | IL3    | external interrupt 3 polarity level |